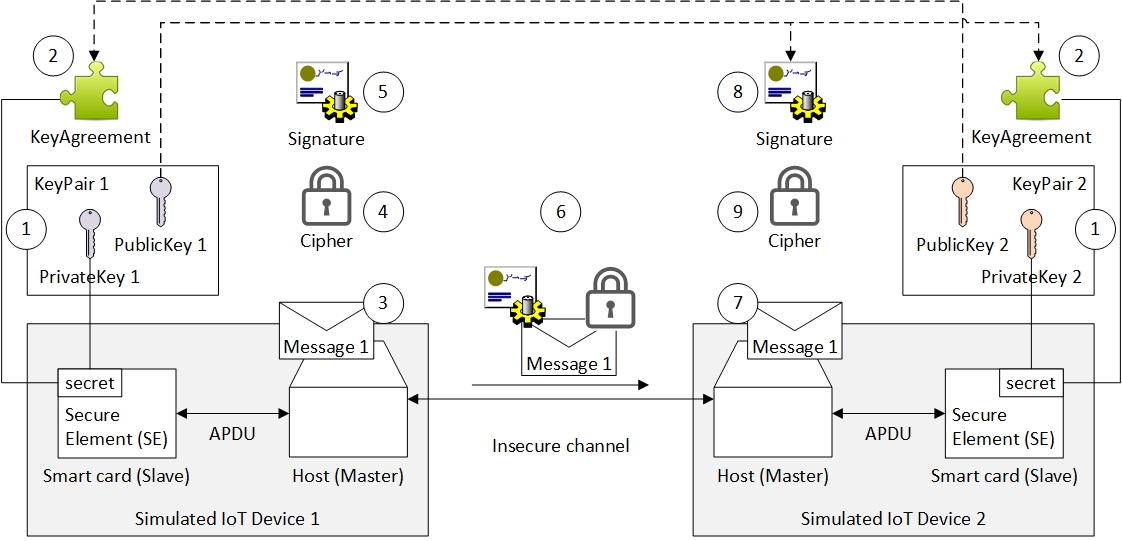

Der grundlegende kryptographische Prozess ist keine Eigenerfindung, sondern stützt auf etablierte kryptographische Vorgänge wie sie aktuell gebräuchlich sind. Die Herausforderung besteht darin, für die Smart Card ein Applet zu Entwickeln das den Prozess geeignet umsetzt.

Zudem wird für den Betrieb des Prozesses nebst der On-Card Umsetzung eine entsprechende Off-Card Implementierung benötigt, die auf dem Computer (Host) betrieben wird. Im Prozess simuliert die Off-Card Implementierung das eine IoT Gerät und das Applet auf der Smart Card das andere.

Da in diesem Arbeitsgebiet der Schwerpunkt in der Erforschung der Möglichkeiten und Grenzen der verwendeten Smart Card liegt, wird dabei auch der Übertragungskanal simuliert. Dies bedeutet, dass der Nachrichtenaustausch auf einem Computer mit seiner integrierten Smart Card stattfindet und diesen nicht verlässt.

Die folgende Abbildung 2 stellt den etablierten, grundlegenden kryptographischen Prozess dar.

Abbildung 2: Etablierter, grundlegender kryptographischer Prozess

Beschreibung des Prozesses und der verwendeten kryptographischen Algorithmen:

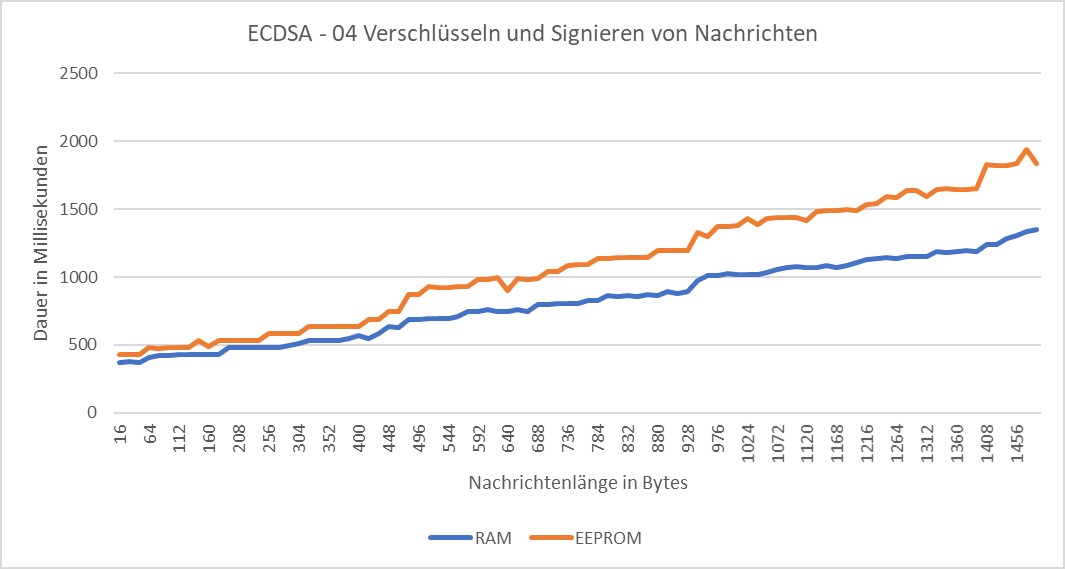

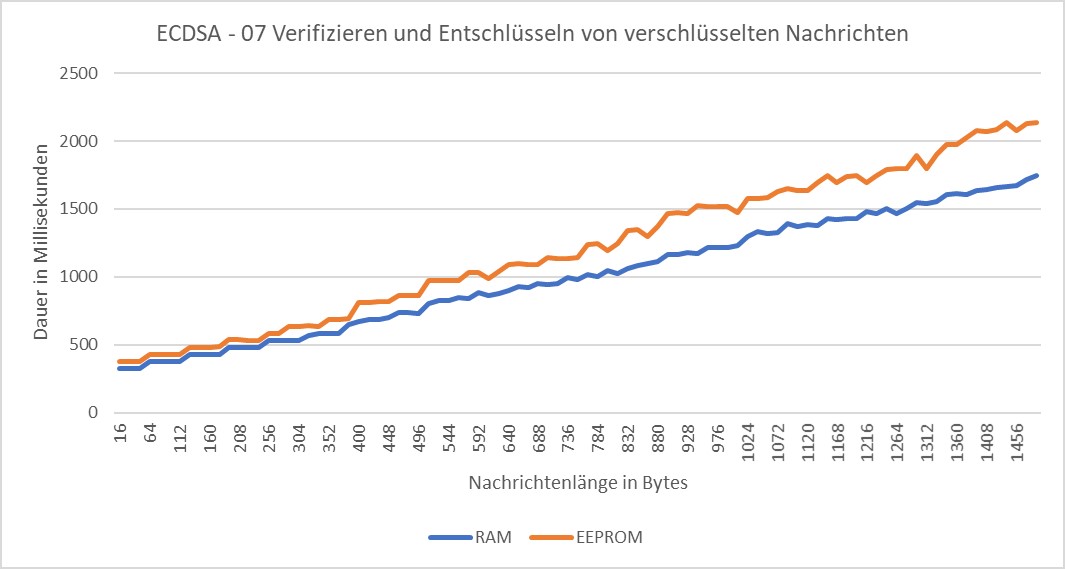

Im dritten Experiment werden die einzelnen Vorgänge soweit als möglich gruppiert ausgeführt. Dadurch ist der Overhead und somit die Ausführungszeit in der Kommunikation zwischen dem IoT Gerät und seiner Smart Card optimiert. Durch den Einsatz des entwickelten Datenfragmentierungsansatzes können von der Smart Card lange Nachrichten behandelt werden. Wird hierfür das schnellere RAM der Smart Card verwendet ist die maximale Nachrichtenlänge auf 1'488 Bytes limitiert. Mit dem langsameren EEPROM Speicher der Smart Card können nahezu 32 kBytes lange Nachrichten mit der Smart Card verarbeitet werden.

Die beiden Liniendiagramme in Abbildung 3 und 4 zeigen die Ausführungszeiten für das verarbeiten von Nachrichten mit Längen zwischen einem und 1'488 Bytes auf der Smart Card. Auch zeigen sie den Zeitunterschied zwischen dem RAM und dem EEPROM.

Abbildung 3: Ausführungszeiten mit RAM und EEPROM für das Verschlüsseln und Signieren

Abbildung 4: Ausführungszeiten mit RAM und EEPROM für die Verifikation und das Entschlüsseln

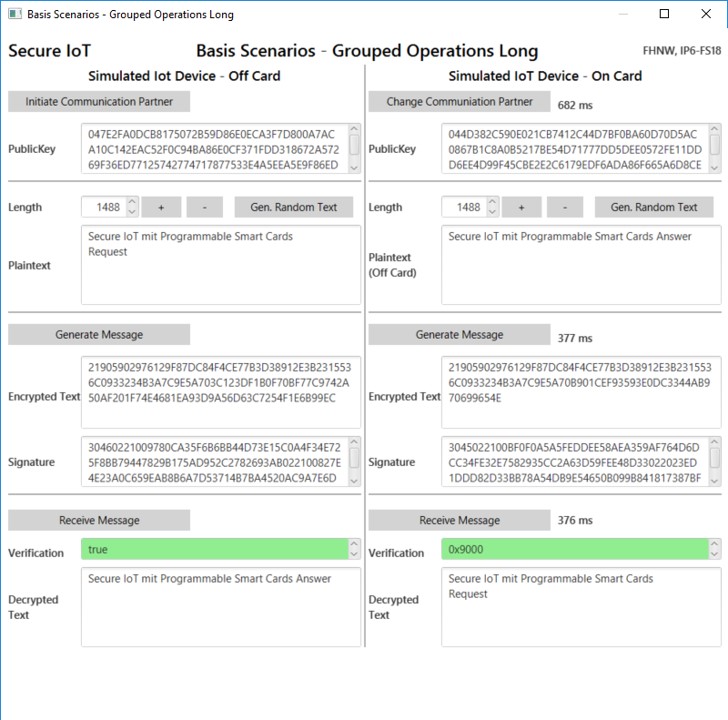

Der nachfolgende Screenshot in Abbildung 5 zeigt wie das dritte Experiment in der Demonstrator Applikation nachvollzogen werden kann.

Abbildung 5: Nachvollziehung des dritten Experiments in der Demonstrator Applikation